## Accellera VHDL-2006

By

# Jim Lewis, SynthWorks VHDL Training jim@synthworks.com

MARLUG - Mid-Atlantic Region Local Users Group ANNUAL CONFERENCE - OCTOBER 12, 2006 Johns Hopkins University Applied Physics Lab – Laurel, MD

| Accellera VHDL-2006                                                                                                                                                                                                    | SynthWorks |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| <ul> <li>IEEE VASG - VHDL-200X effort</li> <li>Started in 2003 and made good technical progress</li> <li>However, no \$\$\$ for LRM editing</li> </ul>                                                                 |            |

| <ul> <li>Accellera VHDL TSC</li> <li>Took over in 2005,</li> <li>Funded the technical editing,</li> <li>Users reviewed and prioritized proposals,</li> <li>Did super-human work to finalize it for DAC 2006</li> </ul> |            |

| <ul> <li><u>* Accellera VHDL-2006 Standard 3.0 *</u></li> <li>• Approved at DAC 2006 by Accellera board</li> <li>• Ready for industry adoption</li> </ul>                                                              |            |

#### Accellera VHDL-2006

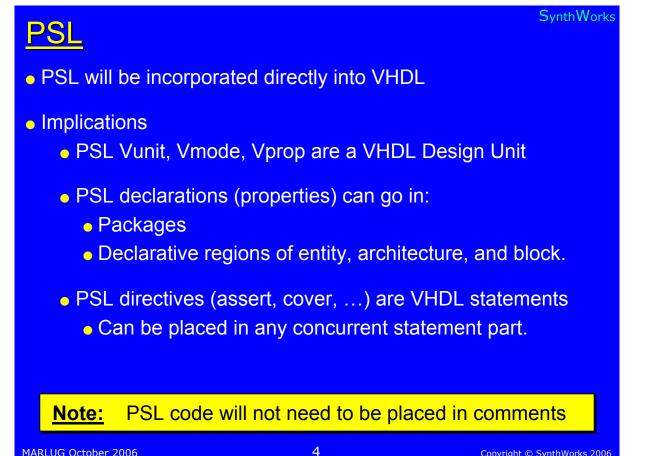

- PSL

- IP Protection via Encryption

- VHDL Procedural Interface VHPI

- Type Generics

- Generics on Packages

- Arrays with unconstrained arrays

- Records with unconstrained arrays

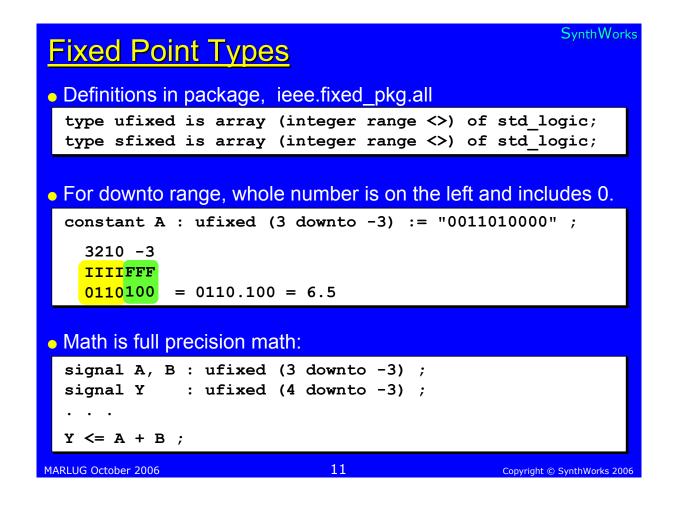

- Fixed Point Packages

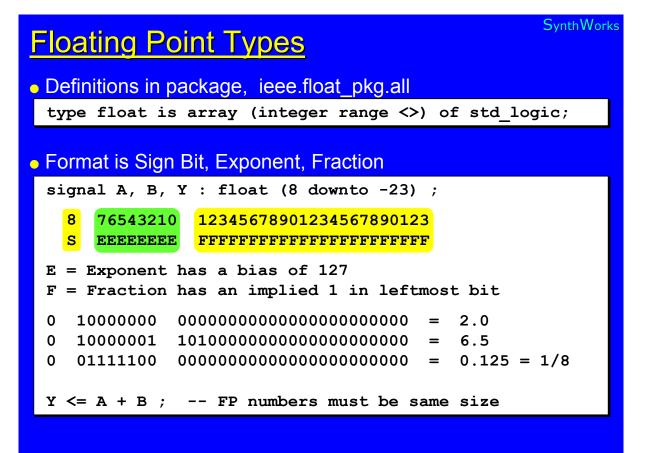

- Floating Point Packages

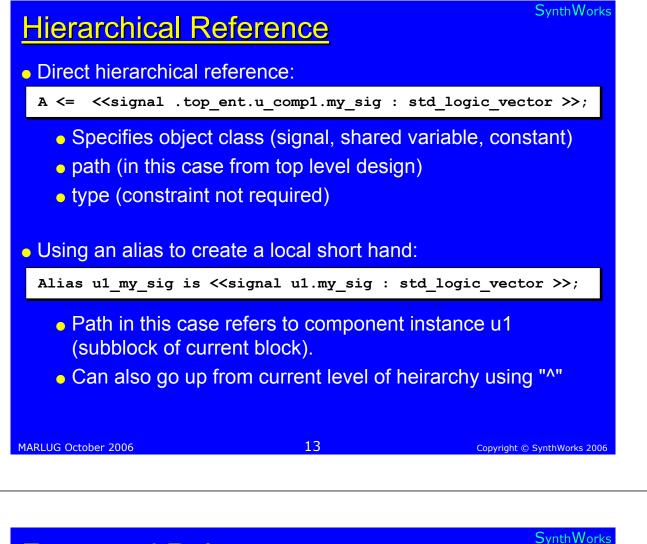

- Hierarchical references of signals

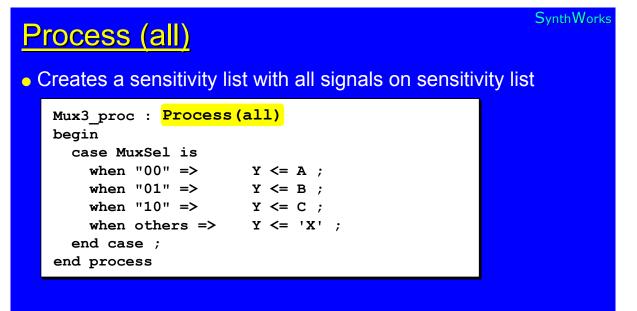

- Process(all)

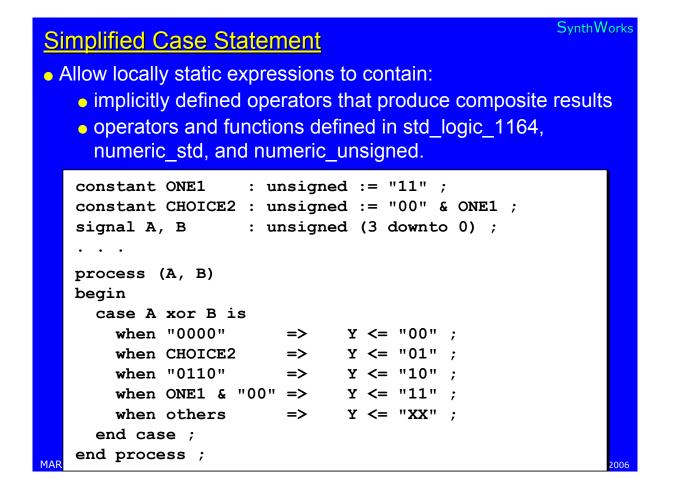

- Simplified Case Statements

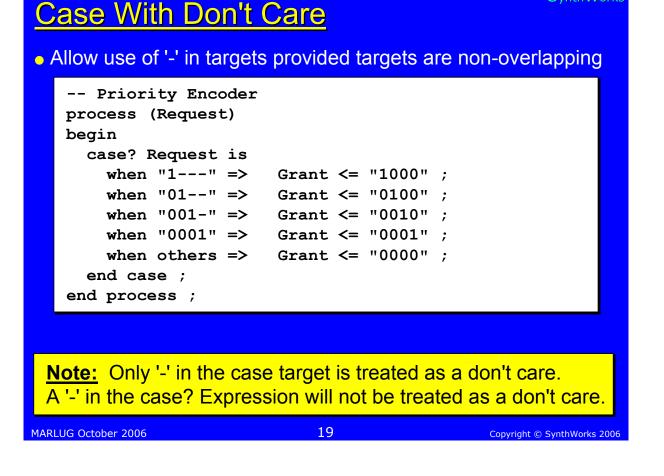

- Don't Care in a Case Statement

- Conditional Expression Updates

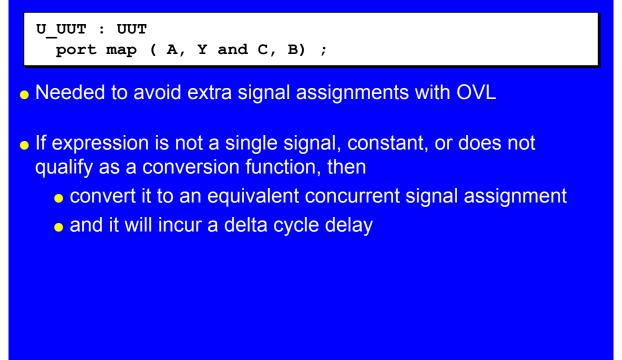

- Expressions in port maps

- Read out ports

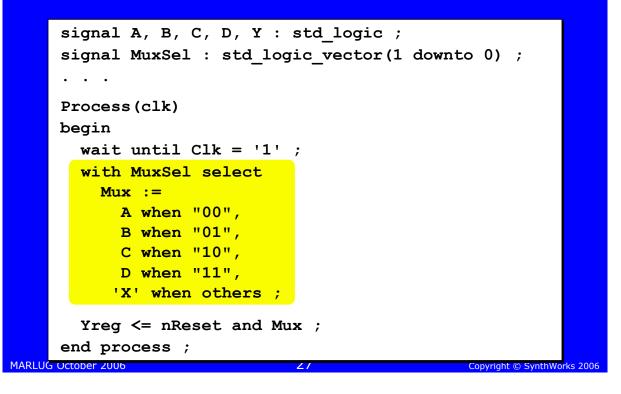

- Conditional and Selected assignment in sequential code

- hwrite, owrite, ... hread, oread

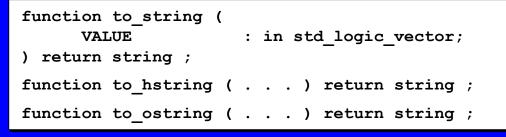

- to string, to hstring, …

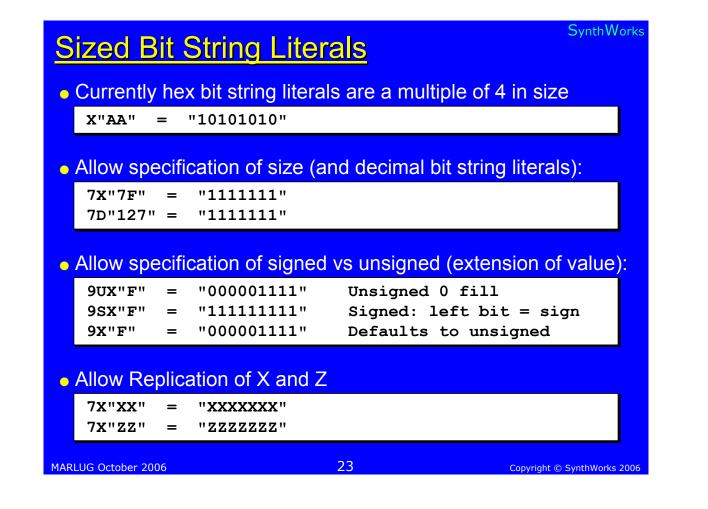

- Sized bit string literals

- Unary Reduction Operators

- Array/Scalar Logic Operators

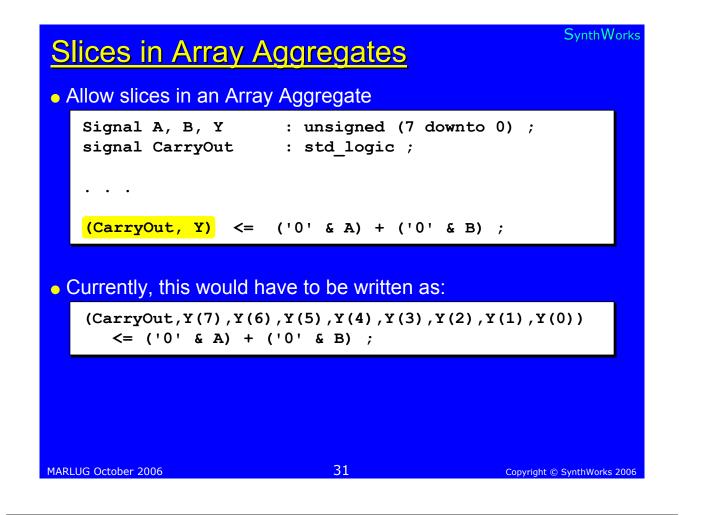

- Slices in array aggregates

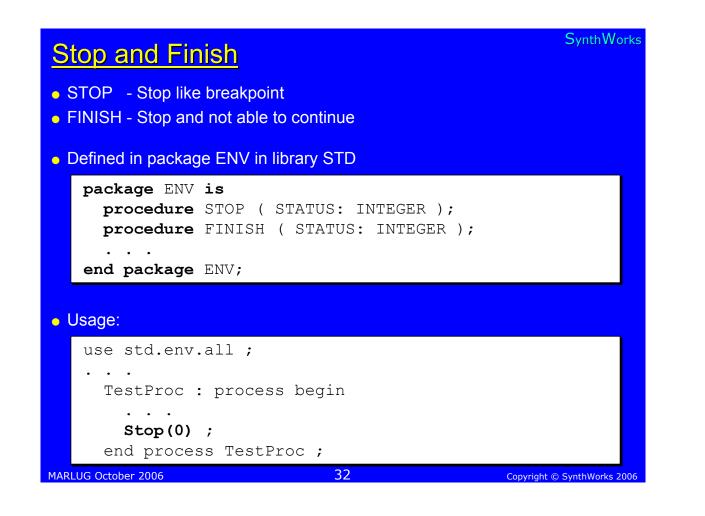

- Stop and Finish

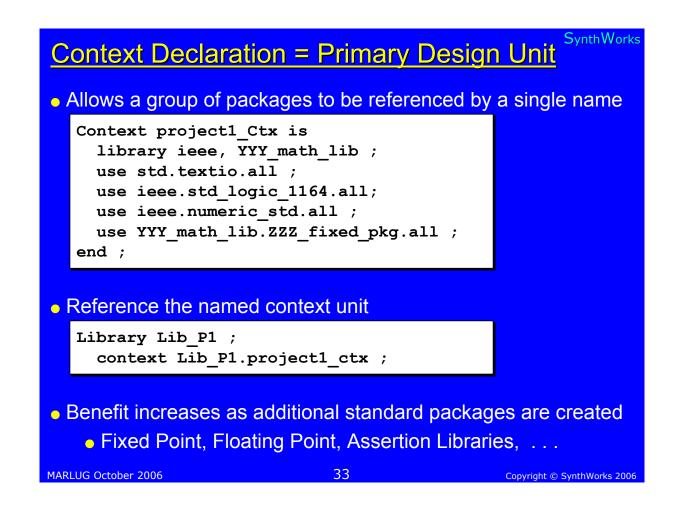

- Context Declarations

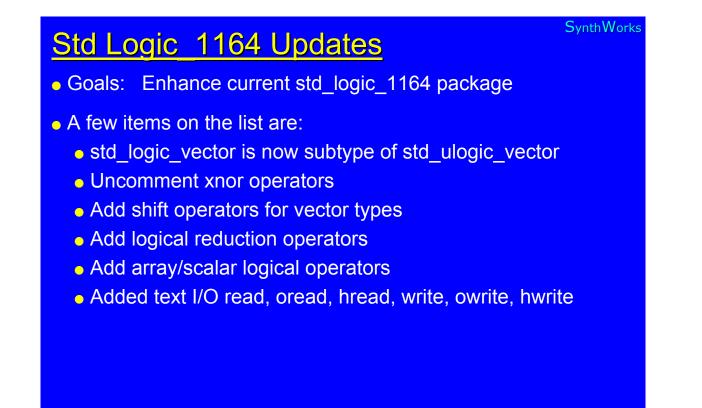

- Std\_logic\_1164 Updates

- Numeric Std Updates

- Numeric\_Std\_Unsigned

Many of VHDL's cumbersome syntax issues were fixed

MARLUG October 2006

Copyright © SynthWorks 2006

#### IP Protection and Encryption

- A pragma-based approach

- Allows IP authors to mark specific areas of VHDL code for encryption using standard algorithms.

- The proposal:

- Defines constructs to demarcate protected envelopes in VHDL source code.

- Defines keywords to specify algorithms and keys.

- Tools that work with encrypted IP must not reveal any details through any interface or output it generates.

- For example, a synthesis tool should generate an encrypted netlist for any portion of a design that is encrypted.

5

```

MARLUG October 2006

```

#### VHDL Procedural Interface - VHPI

- Standardized Procedural Programming Interface to VHDL

- Gives access to information about a VHDL model during analysis, elaboration, and execution.

- For add-in tools such as linters, profilers, code coverage, timing and power analyzers, and

- For connecting in external models

- Object-oriented C model.

- Gives direct access as well as callback functions for when an event occurs.

Copyright © SynthWorks 2006

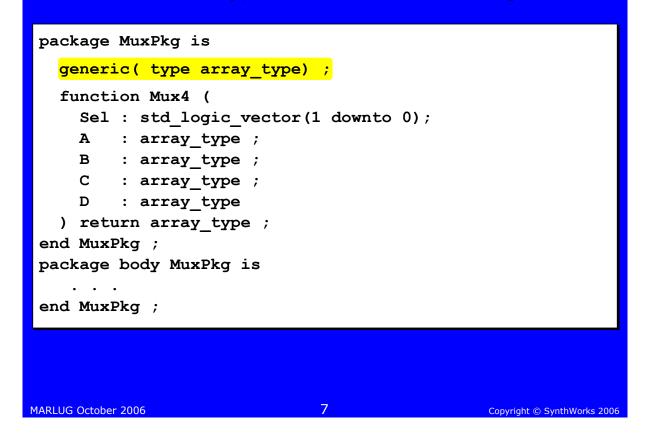

#### Formal Generics Types + Generics on Packages

#### Formal Generics Types + Generics on Packages

Making the Mux4 function available for both std\_logic\_vector and unsigned.

```

library ieee ;

package MuxPkg_slv is new work.MuxPkg

Generic map (

array_type => ieee.std_logic_1164.std_logic_vector

) ;

library ieee ;

package MuxPkg_unsigned is new work.MuxPkg

Generic map (

array_type => ieee.numeric_std.unsigned

) ;

```

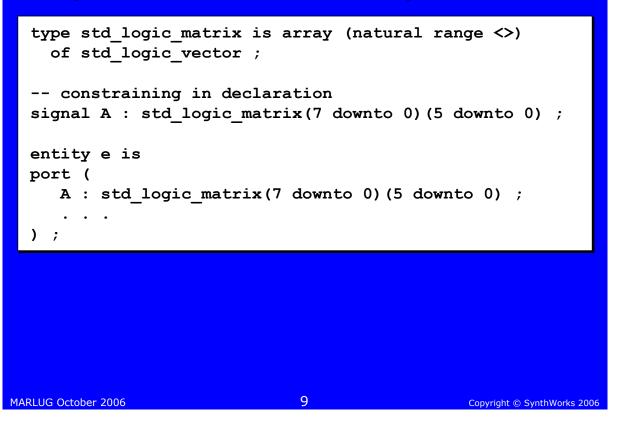

### Arrays of Unconstrained Arrays

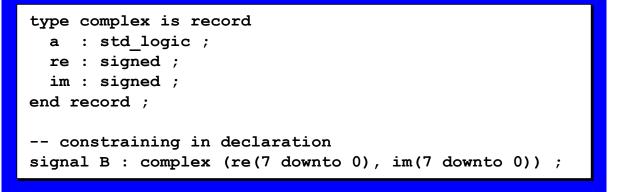

### Records of Unconstrained Arrays

SynthWorks

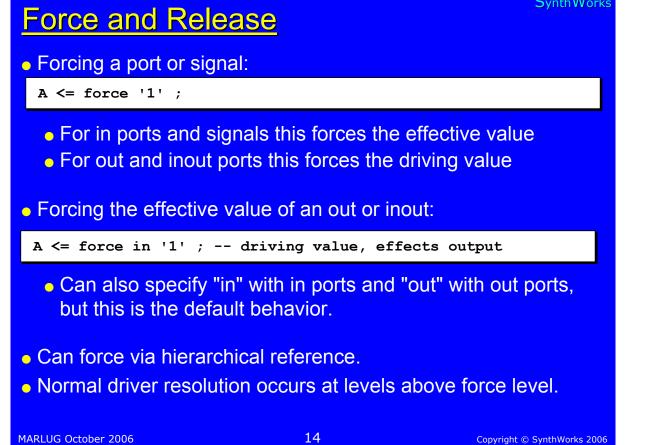

| Force and Release   | 2  |         | SynthWorks           |

|---------------------|----|---------|----------------------|

| Releasing a signal: |    |         |                      |

| A <= release ;      |    |         |                      |

|                     |    |         |                      |

|                     |    |         |                      |

|                     |    |         |                      |

|                     |    |         |                      |

|                     |    |         |                      |

|                     |    |         |                      |

|                     |    |         |                      |

|                     |    |         |                      |

| MARLUG October 2006 | 15 | Copyrig | ht © SynthWorks 2006 |

• Benefit: Reduce mismatches between simulation and synthesis

#### Simplified Case Statement

Although concatenation is specifically allowed, some cases will still require a type qualifier.

```

signal A, B, C, D : std_logic ;

. . .

process (A, B, C, D)

begin

case std_logic_vector'(A & B & C & D) is

when "0000" => Y <= "00" ;

when "0011" => Y <= "01" ;

when "0110" => Y <= "10" ;

when "1100" => Y <= "11" ;

when others => Y <= "XX" ;

end case ;

end process ;</pre>

```

• Current VHDL syntax:

if (Cs1='1' and nCs2='0' and Addr=X"A5") then

if nWe = '0' then

• New: Allow top level of condition to be std\_ulogic or bit:

```

if (Cs1 and not nCs2 and Cs3) then

if (not nWe) then

```

Create special comparison operators that return std\_ulogic (?=, ?/=, ?>, ?>=, ?<, ?<=)</li>

if (Cs1 and not nCs2 and Addr?=X"A5") then

DevSel1 <= Cs1 and not nCs2 and Addr?=X"A5" ;</pre>

```

Does not mask 'X'

```

MARLUG October 2006

#### Hwrite, Hread, Owrite, Oread

Support Hex and Octal read & write for all bit based array types

| procedure hwrite (                          |                                            |

|---------------------------------------------|--------------------------------------------|

| Buf                                         | : inout Line ;                             |

| VALUE                                       | : in bit_vector ;                          |

| JUSTIFIED                                   | : in SIDE := RIGHT;                        |

| FIELD                                       | : in WIDTH := 0                            |

| );                                          |                                            |

| procedure hread (                           |                                            |

| Buf                                         | : inout Line ;                             |

| VALUE                                       | : out bit_vector ;                         |

| Good                                        | : out boolean                              |

| );                                          |                                            |

| procedure oread ( .<br>procedure owrite ( . |                                            |

| • No new packages. Su                       | ipported in base package                   |

| For backward comp                           | oatibility, std_logic_textio will be empty |

| MARLUG October 2006                         | 21 Copyright © SynthWorks 2006             |

### <u>To String, To HString, To OString</u>

- Create to\_string for all types.

- Create hex and octal functions for all bit based array types

#### Formatting Output with Write (not write from TextIO):

```

write(Output, "%%%ERROR data value miscompare." &

LF & " Actual value = " & to_hstring (Data) &

LF & " Expected value = " & to_hstring (ExpData) &

LF & " at time: " & to_string (now, right, 12)) ;

```

#### Read Output Ports

Read output ports

- Value read will be locally driven value

- Assertions need to be able to read output ports

MARLUG October 2006 25 Copyright © SynthWorks 2006

### Allow Conditional Assignments for Signals and Variables in Sequential Code

Statemachine code:

if (FP = '1') then

NextState <= FLASH ;

else

NextState <= IDLE ;

end if ;</pre>

#### • Simplification (new part is that this is in a process):

NextState <= FLASH when (FP = '1') else IDLE ;

• Also support conditional variable assignment:

NextState := FLASH when (FP = '1') else IDLE ;

### Allow Selected Assignments for Signals and Variables in Sequential Code

| <u>Unary R</u>           | <u>educt</u>                                             | ion Opera                               | ators                                           | SynthWorl              |

|--------------------------|----------------------------------------------------------|-----------------------------------------|-------------------------------------------------|------------------------|

| Define unar              | y AND,                                                   | OR, XOR, NA                             | ND, NOR, XN                                     | IOR                    |

| function                 | "and"                                                    | ( anonymous:                            | BIT_VECTOR)                                     | return BIT;            |

| function                 | "or"                                                     | ( anonymous:                            | BIT_VECTOR)                                     | <pre>return BIT;</pre> |

| function                 | "nand"                                                   | ( anonymous:                            | BIT_VECTOR)                                     | <pre>return BIT;</pre> |

| function                 | "nor"                                                    | ( anonymous:                            | BIT_VECTOR)                                     | return BIT;            |

| function                 | "xor"                                                    | ( anonymous:                            | BIT_VECTOR)                                     | return BIT;            |

| function                 | "xnor"                                                   | ( anonymous:                            | BIT_VECTOR)                                     | <pre>return BIT;</pre> |

|                          |                                                          |                                         |                                                 |                        |

| Calculating<br>Parity <= |                                                          | ith reduction o                         | operators:                                      |                        |

| Parity <=                | <mark>xor</mark> Da                                      |                                         |                                                 |                        |

| Parity <=                | xor Da                                                   | ta ;<br>ithout reductio                 |                                                 | ) xor                  |

| Parity <=                | <b>xor</b> Da<br>Parity w<br>Data (7)                    | ta ;<br>ithout reductio<br>) xor Data(6 | on operators:                                   |                        |

| Parity <=                | <b>xor</b> Da<br><b>Parity w</b><br>Data (7)<br>Data (4) | ta ;<br>ithout reductio<br>) xor Data(6 | ON OPERATORS:<br>) xor Data(5)<br>) xor Data(2) |                        |

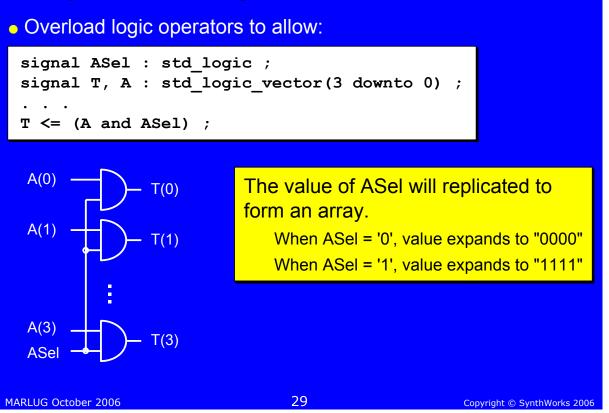

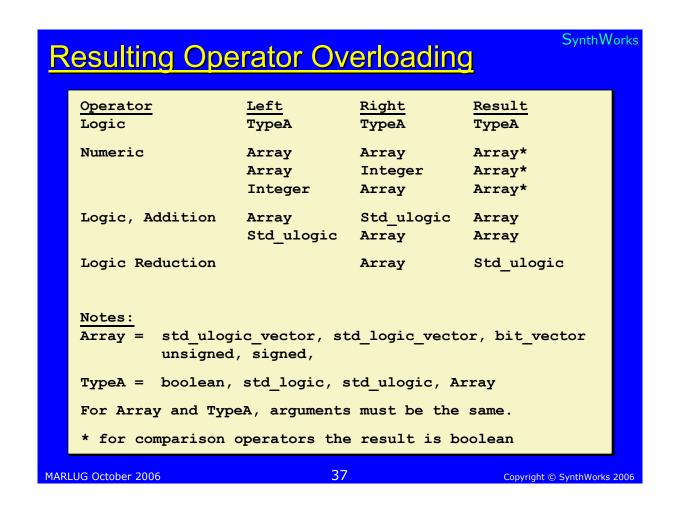

### Array / Scalar Logic Operators

#

#### Numeric Std Updates

• Goals:

- Enhance current numeric\_std package.

- Unsigned math with std\_logic\_vector/std\_ulogic\_vector

#### • A few items on the numeric\_std list are:

- Array / scalar addition operators

- TO\_X01, IS\_X for unsigned and signed

- Logic reduction operators

- Array / scalar logic operators

- TextIO for numeric\_std

MARLUG October 2006

### Numeric Std Unsigned

Overloads for std\_ulogic\_vector to have all of the operators defined for ieee.numeric\_std.unsigned

35

Replacement for std\_logic\_unsigned that is consistent with numeric\_std

Copyright © SynthWorks 2006

#### SynthWorks VHDL Standards Next Steps Constrained Random Stimulus Generation Random value generation with dynamic weighting Randomly generate sequences of stimulus Functional Coverage Interfaces Verification Data Structures: associative arrays, queues, FIFOs, and memories Direct C and Verilog/SystemVerilog Calls Object Orientation Goal = HDVL: Hardware Description and Verification Language Full verification capabilities in one consistent language 38 MARLUG October 2006 Copyright © SynthWorks 2006

### SynthWorks & VHDL Standards

At SynthWorks, we are committed to see that VHDL is updated to incorporate the good features/concepts from other HDL/HVL languages such as SystemVerilog, E (specman), and Vera.

- At SynthWorks, we invest 100's of hours each year working on VHDL's standards

- Support VHDL's standards efforts by:

- Encouraging your EDA vendor(s) to support VHDL standards,

- Participating in VHDL standards working groups, and / or

- Purchasing your VHDL training from SynthWorks

#### SynthWorks VHDL Training

Comprehensive VHDL Introduction 4 Days http://www.synthworks.com/comprehensive vhdl introduction.htm A design and verification engineer's introduction to VHDL syntax, RTL coding, and testbenches. Students get VHDL hardware experience with our FPGA based lab board. VHDL Testbenches and Verification 3 days http://www.synthworks.com/vhdl testbench verification.htm Learn to simplify writing tests by creating transaction-based testbenches. Intermediate VHDL Coding for Synthesis 2 Days http://www.synthworks.com/intermediate\_vhdl\_synthesis.htm Learn RTL (hardware) coding styles that produce better, faster, and smaller logic. Advanced VHDL Coding for Synthesis 2 Days http://www.synthworks.com/advanced vhdl synthesis.htm Learn to avoid RTL coding issues, problem solving techniques, and advanced VHDL constructs.

For additional courses see: <u>http://www.synthworks.com</u>